存储管理

存储管理

TLB基本原理

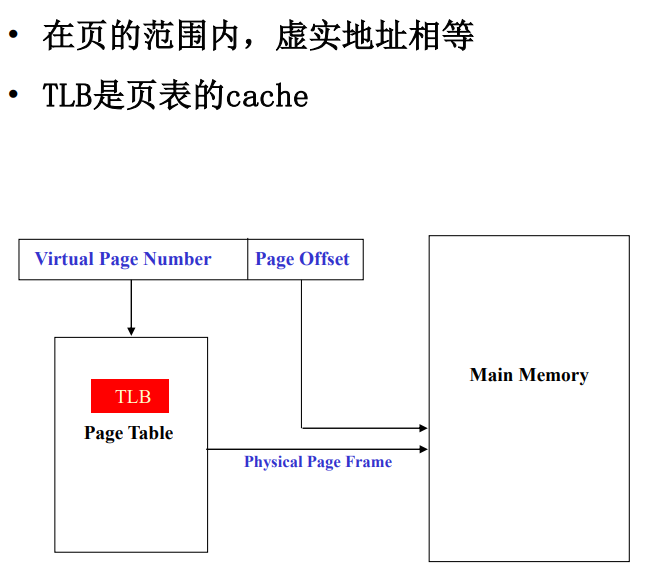

TLB实际上是操作系统中页表的Cache

TLB主要负责完成用户空间到物理空间的转化

- 一般与Cache访问同时进行

- TLB内容:虚地址(Cache的Tag),物理地址(Cache的 Data),保护位(Cache的状态)

- TLB失效处理 • TLB失效时需要把相应页表内容从内存取到TLB

- TLB失效时硬件(如X86的page walker)和软件(如MIPS的特殊例外)来填充TLB

TLB例外类型

Refill :

如果查找TLB没有找到一个虚地址匹配(VPN2+ASID/G)

例外入口:80000000 (除非exl=1) (由于TLB失效比较频繁,这里是一个单独的例外入口,不用查找,比较快)

TLB invalid

- 如果找到一个虚地址匹配项,但其v=0(无效)

- 例外入口:80000180

- 细分为两种:TLBL for loads, TLBS for stores

TLB modify :

如果找到一个虚地址匹配项,其v=1,但D=0且访问为store

例外入口80000180

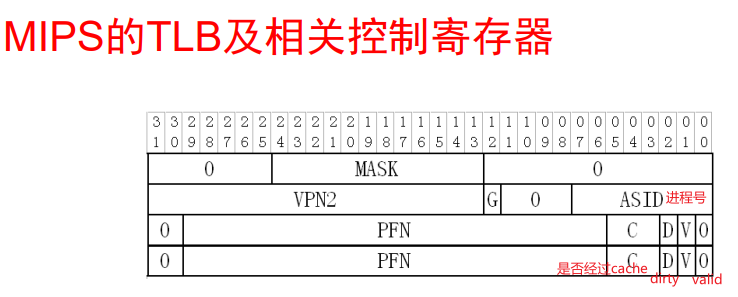

mips tlb

TLB一项对应两个连续的物理地址(一个虚拟地址对应两项)

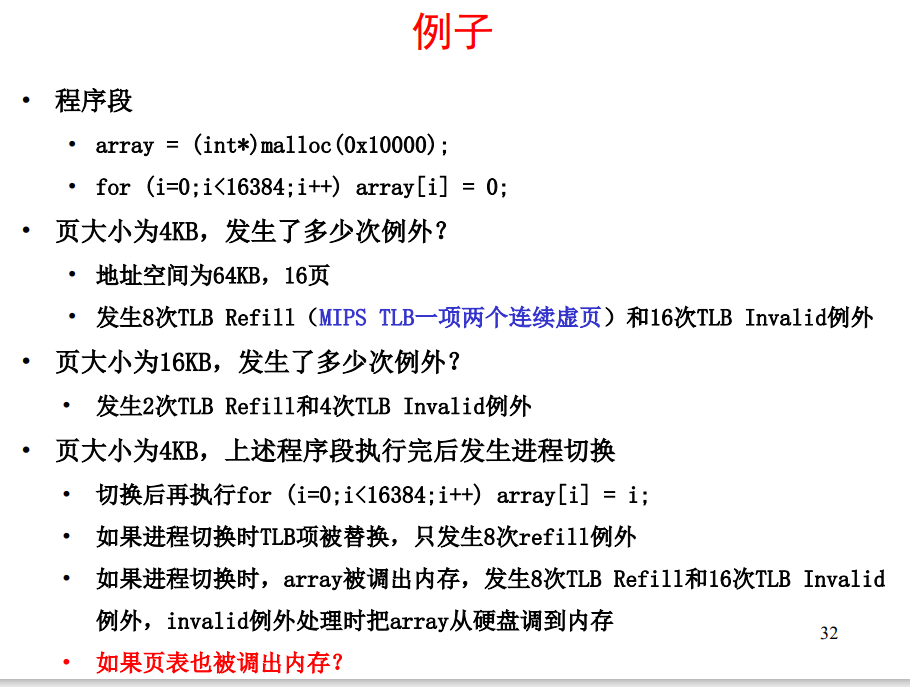

TLB例外次数计算

1 | Array=(int*)malloc(0x1000) |

执行上面的语句后, 用户程序malloc(0x1000)返回虚地址0x450000

操作系统在该进程的vma_struct链表中记录地址范围0x450000-0x4501000为已 分配地址,可读可写。此时分配了虚拟地址但是物理地址还没有分配。

1 | For (I=0;I<1024;I++) Array[i] = 0 |

用户程序试图写0x450000,TLB查找失败,引起一次 tlb refill例外

Tlb refill从相应页表位置取入页表内容填入TLB。但该页表还没初始化

例外返回到用户程序,重新开始访问 :TLB表项找到,但是无效,发生TLB Invalid例外

操作系统查找vma_struct,判断该地址已分配,处于可写状态,因此为它分配物理页面,并将物理地址填入页表,更新TLB ,例外返回,写操作再次重试,成功。

用户程序继续写0x450004,008…,因为TLB项已经存在,将全速运行,除非中间 发生进程切换导致其TLB项被换出。如果发生被换出的情况,再次运行时将发生 refill例外从页表取得有效内容,不会再发生invalid例外(refill例外频率>>invalid))

为什么要分成两次例外

因为TLB更容易失效,而内存(比较大)相对不容易失效。

TLB verilog简单实现

1 | module tlb_cam(vpn_in, pfn_out, hit, valid_out); |